# Interface Passivation and Trap Reduction via a Solution-Based Method for Near-Zero Hysteresis Nanowire Field-Effect Transistors

Marios Constantinou,<sup>†</sup> Vlad Stolojan,<sup>†</sup> Kiron Prabha Rajeev,<sup>†</sup> Steven Hinder,<sup>‡</sup> Brett Fisher,<sup>†</sup> Timothy D. Bogart,<sup>§</sup> Brian A. Korgel,<sup>§</sup> and Maxim Shkunov<sup>\*,†</sup>

<sup>†</sup>Advanced Technology Institute, Electronic and Electrical Engineering and <sup>‡</sup>Department of Mechanical Engineering Sciences, University of Surrey, Guildford, Surrey GU2 7HX, U.K.

<sup>§</sup>Department of Chemical Engineering, Texas Materials Institute and Center for Nano and Molecular Science and Technology, The University of Texas, Austin, Texas 78712-1062, United States

# Supporting Information

**ABSTRACT:** In this letter, we demonstrate a solution-based method for a one-step deposition and surface passivation of the as-grown silicon nanowires (Si NWs). Using *N*,*N*-dimethylformamide (DMF) as a mild oxidizing agent, the NWs' surface traps density was reduced by over 2 orders of magnitude from  $1 \times 10^{13}$  cm<sup>-2</sup> in pristine NWs to  $3.7 \times 10^{10}$  cm<sup>-2</sup> in DMF-treated NWs, leading to a dramatic hysteresis reduction in NW field-effect transistors (FETs) from up to 32 V to a near-zero hysteresis. The change of the polyphenylsilane NW shell stoichiometric composition was confirmed by X-ray photoelectron spectroscopy analysis showing a 35% increase in

fully oxidized Si<sup>4+</sup> species for DMF-treated NWs compared to dry NW powder. Additionally, a shell oxidation effect induced by DMF resulted is a more stable NW FET performance with steady transistor currents and only 1.5 V hysteresis after 1000 h of air exposure.

**KEYWORDS:** hysteresis, silicon nanowires, field-effect transistor, nanowire interface, DMF, XPS, interface trap reduction, interface passivation

Cilicon nanowires (Si NWs) are attractive candidates for solvent-based processing. Their unique physical and electrical properties, including single-crystal lattice structure, efficient charge-transport capabilities, and excellent mechanical flexibility,<sup>1</sup> attracted considerable research attention for the fabrication of chemical and biological sensors,<sup>2–4</sup> high-performance field-effect transistors (FETs),<sup>5-7</sup> and optical devices.<sup>7</sup> Leiber's group has demonstrated a charge mobility of 1350 cm<sup>2</sup>  $V^{-1} s^{-1}$  using boron-doped chemical vapor deposition (CVD)grown Si NWs as semiconducting materials in the FETs, emphasizing the potential for high-mobility devices.<sup>5</sup> Oriented Si NWs can be printed and solution-processed on electrode structures on flexible substrates using various deposition techniques,<sup>1</sup> suitable for the production of electronic devices on a roll-to-roll basis for industrial applications. This highlights their compatibility with low-temperature processing steps for plastic and printed electronic device applications such as artificial e-skin<sup>8</sup> and chemical sensors.<sup>9</sup>

To enable truly large area printed electric devices incorporating semiconducting nanowires (NWs), a scalable NW growth technology is required. CVD-based growth methods struggle to deliver significant amounts of NW powder because of limited substrate size and the high cost of growth processes. On the contrary, a supercritical fluid–liquid–solid (SFLS) method<sup>10</sup> has the ability to tune the NW synthesis and to be scaled-up for kilogram per day production, suitable for industrial applications.<sup>11</sup> However, the SFLS-grown Si NWs are covered with an amorphous polyphenylsilane shell during the synthesis. The shell is mostly composed of carbon, oxygen, and silicon species, as we discuss later, with silicon being in various oxidation states (Si<sup>+</sup>, Si<sup>2+</sup>, Si<sup>3+</sup>, and Si<sup>4+</sup>), contributing to the NW surface states that play an important role in the electronic properties, and can dramatically affect the NW device performance such as in FETs. Trapping of the charge carriers at the semiconductor/dielectric interface, including the NW shell region, can lead to a hysteresis effect in devices I–V characteristics and low charge mobility.

Hysteresis in the NW, carbon nanotube, and organic-based FETs, especially utilizing SiO<sub>2</sub> dielectrics, is the main source for performance instabilities that affect the reproducibility and reliability of the devices. Hysteresis represents a shift in the threshold voltage ( $V_{\rm th}$ ) under the application of gate bias.

The hysteresis behavior mainly originates from electron and hole trapping/detrapping at the semiconductor/insulator

Received:August 3, 2015Accepted:September 24, 2015Published:September 24, 2015

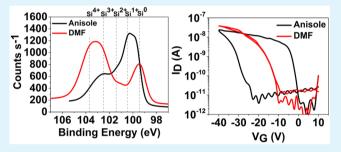

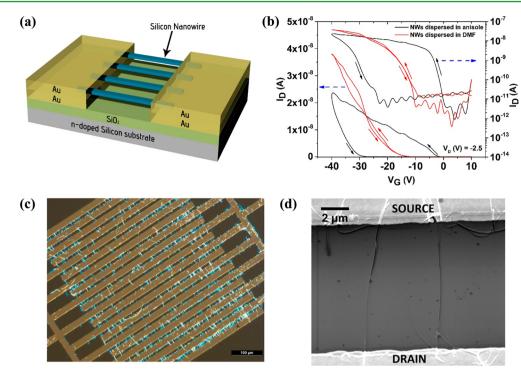

**Figure 1.** (a) Schematic diagram of the FET device showing the NWs aligned across the channel area and the double-layer gold ohmic contacts, where a doped silicon substrate serves as the common gate electrode. (b) Transfer characteristics of the bottom-gated Si NW FET shown in linear and log-linear scales. The arrows show the direction of the gate voltage scan. A high hysteresis of 30 V (black line) was exhibited when NWs are dispersed in anisole and a very low hysteresis of 0.9 V when NWs are dispersed in DMF (red line) because of significant reduction of the hole traps. POM (c) and SEM (d) images of a typical FET device used in this work with Si NWs aligned across a 10  $\mu$ m gap between gold electrodes.

interface due to dielectric surface functionalities and adsorbed small molecules (e.g., oxygen and water) by the silanol groups at the interfacial layer between the semiconducting material and the gate dielectric.<sup>12</sup> These silanol groups (Si–OH), also known as hydroxyl groups, can be formed at the silicon oxide surface even during the synthesis of silica<sup>13</sup> and not just through atmospheric exposure. A high density of water molecules at the SiO<sub>2</sub> surface was shown to induce a hysteresis exceeding 50% of the applied gate voltage in carbon nanotube FETs.<sup>14</sup> Additionally, hole trapping can originate from weak Si–Si bonds (excess silicon or oxygen vacancies) and weak Si–O bonds (siloxanes) near the Si/SiO<sub>2</sub> interface.<sup>15</sup>

In NW FETs, hysteresis can be observed in both moisturefree (dry glovebox) and ambient air conditions and is associated with strong bonding of polar water molecules to SiO<sub>2</sub> surfaces of NWs and substrates.

Annealing Si NWs at 700<sup>16</sup> and ~1100 °C<sup>17</sup> in an oxygen environment was reported to form a SiO<sub>2</sub> passivation layer around the NWs, reducing the hysteresis caused by the surface states. Fukata et al.<sup>18</sup> demonstrated thermal oxidation using ozone to form a thick, good-quality SiO<sub>2</sub> layer on Si NWs at a lower temperature of 600 °C. However, such high-temperature annealing is not suitable for plastic electronic applications, and a low-temperature process is still required.

In this work, the hysteresis effect in solution-processed SFLSgrown Si NW FET devices was investigated, and a roomtemperature solvent-based oxidizing-agent treatment was applied to demonstrate reproducible bottom-gated NW FETs with very low/near-zero hysteresis. The choice of solvents had a dramatic impact on the NW surface traps, and as shown for *N*,*N*-dimethylformamide (DMF), the trap density was reduced by over 2 orders of magnitude.

The undoped (intrinsic) Si NWs were grown via SFLS with monophenylsilane as a reactant in supercritical organic solvents.<sup>10</sup> The Si NWs have a single-crystal silicon core and an amorphous polyphenylsilane shell mainly composed of carbon (C 1s, 44%), oxygen (O 1s, 39%), and stoichiometric silicon (Si 2p, 15%), as verified by our X-ray photoelectron spectroscopy (XPS) analysis (Figure S2 and Table S1 in the Supporting Information, SI) and consistent with previous reports.<sup>11</sup> We used a bottom-gated FET configuration, where the NWs were deposited and aligned between device electrodes in a one-step process using dielectrophoretic self-alignment of NWs dispersed in a solvent with the application of an alternating electric field<sup>19</sup> (see the SI for the device's fabrication). The complete device structure is shown in Figure 1a. Over 15 solvents were investigated to produce dispersions of NWs, but only DMF and dimethylacetamide (DMA) have shown pronounced NW oxidation/passivation effects resulting in significant improvement of the NW transistor performance. For the studies presented in this paper, anisole was used as the reference solvent for NW dispersions. Parts c and d of Figure 1 show polarized optical microscopy (POM) and scanning electron microscopy (SEM) images of a typical Si NW FET device used in this work.

NW FETs were characterized using a Kiethley 4200 SCS semiconductor parameter analyzer in a dry  $N_2$ -filled glovebox to eliminate environmental effects causing degradation of the devices, and stability measurements were conducted in ambient air conditions. The change of the gate bias sweeping direction from forward to backward induced a shift in the threshold voltage, which was estimated for extraction of the hysteresis value (see the SI for NW hysteresis measurements).

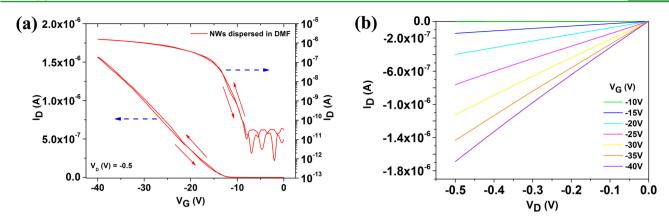

Figure 2. I-V characteristics of DMF-treated Si NW FETs with 15 NWs in the channel. (a) Transfer characteristics obtained at  $V_D = -0.5$  V showing a very low hysteresis of 0.1 V and a device mobility of 15 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> (eq 3). (b) Output characteristics showing an ohmic linear behavior of drain current versus drain voltage bias and also good gate modulation.  $V_G$  is increased in -5 V steps from -10 to -40 V.

The hysteresis values were obtained as the magnitude of the threshold voltage shift during the forward  $(V_{\rm th\ forward})$  and reverse  $(V_{\rm th\ reverse})$  sweeps of the gate voltage  $(V_{\rm G})$ :  $\Delta V_{\rm th} = V_{\rm th\ reverse} - V_{\rm th\ forward}$ . Hysteresis is associated with the traps through the relationship  $\Delta V_{\rm th} = \Delta Q_{\rm trap}/C_{\nu}^{20}$  where  $\Delta Q_{\rm trap}$  is the amount of trapped charge and  $C_{\rm i}$  is the capacitance of the gate insulator.

The hysteresis values were extracted from the linear-regime FET transfer characteristics (Figure S1 in the SI).

Figure 1b demonstrates typical transfer characteristic data for Si NW FETs prepared using anisole and DMF as processing solvents. Anisole-processed NW FETs showed very large threshold voltage shifts for forward and reverse gate voltage scans, whereas DMF-processed devices demonstrated very small changes between the forward/reverse scans, and the transistor current at higher gate voltages ( $V_{\rm G} = -25$  to -40 V) was typically higher than the current in devices with anisoledispersed NWs. The difference in hysteresis is significant and is attributed to the reaction of the dispersion solvent with the NW shell. Over 100 devices were fabricated and characterized during this work, and all of them showed the consistent trend where devices fabricated using DMF as a solvent exhibited a significant reduction in hysteresis compared to transistors fabricated with anisole. On the basis of a statistical analysis of 15 typical bottom-gated FET devices prepared with each solvent, the average hysteresis values ( $\Delta V_{\rm th}$ ) of NWs dispersed in DMF and anisole were 3 and 25 V, respectively (Figure S3a and Table S2 in the SI).

The charge trap density  $(Q_{trap})$  and the carrier mobility  $(\mu)$  were estimated using the following equations:<sup>6,21–23</sup>

$$qQ_{\rm trap} = \frac{C_{\rm NW} |\Delta V_{\rm th}|}{2\pi (Nr_{\rm nw})L}$$

(1)

$$C_{\rm NW} = N \frac{2\pi\varepsilon_0 \varepsilon_r L}{\cosh^{-1} \left( \frac{r_{\rm nw} + d}{r_{\rm nw}} \right)}$$

(2)

$$\mu = \frac{L^2}{C_{\rm NW}} \frac{1}{V_{\rm D}} g_{\rm m} \tag{3}$$

where q is the elementary charge,  $C_{\rm NW}$  is the total gate capacitance based on the cylinder-on-plate model, which takes into consideration the electrostatic fringing effect,  $^{6,22} \Delta V_{\rm th}$  is the hysteresis, N is the number of NWs crossing the FET

channel,  $r_{\rm nw}$  is the radius of the NW [~15 nm, transmission electron microscopy (TEM) results], *L* is the length of the NW in the FET channel (10  $\mu$ m),  $\varepsilon_0$  is the absolute permittivity,  $\varepsilon_{\rm r}$  is the dielectric constant of the gate insulator (~3.9), and *d* is the thickness of the gate dielectric (~230 nm). In eq 3,  $g_{\rm m}$  is the transconductance ( $g_{\rm m} = \partial I_{\rm D}/\partial V_{\rm G}$ ) and  $V_{\rm D}$  is the applied source–drain voltage. Equation 1 was modified, taking into consideration the total number (*N*) of aligned NWs across the channel.

The density of occupied traps for the devices shown in Figure 1b was calculated using eqs 1 and 2. A Q<sub>trap</sub> value of 1.2  $\times 10^{13}$  cm<sup>-2</sup> was found for the anisole-treated NW FET, with  $\sim$ 120 NWs in the FET channel, whereas the trap density in the DMF-treated NW FET (with ~40 NWs) was  $3.7 \times 10^{11}$  cm<sup>-2</sup> demonstrating significant reduction of traps following DMF passivation. The results for one of the lowest trap densities, 3.7  $\times$  10<sup>10</sup> cm<sup>-2</sup> achieved with DMF-dispersed NW FETs (Figure 2a,b), showed near-zero hysteresis of 0.1 V and ohmic output characteristics. Statistical analysis of over 30 NW FETs fabricated with anisole and DMF solvents demonstrated relatively widespread hysteresis values ( $\Delta V_{th}$ ) between 21 and 32 V corresponding to trap densities from 8.6  $\times$  10<sup>12</sup> to 1.3  $\times$  $10^{13}$  cm<sup>-2</sup> for anisole-dispersed NWs (Figure S3a in the SI). On the contrary, the DMF-dispersed NW FETs showed significantly narrower hysteresis results between 0.1 and 5.1 V corresponding to  $Q_{trap}$  values from 3.7  $\times$  10<sup>10</sup> to 2.1  $\times$  10<sup>12</sup>  $cm^{-2}$  (Figure S3b in the SI).

The hysteresis effect was also investigated for NW devices exposed to ambient air for prolonged periods of time.  $\Delta V_{\rm th}$  was monitored for DMF-treated FETs for over 1000 h, and the hysteresis has steadily reduced from 8 to 1.5 V during this period (Figure S3c,e in the SI), indicating good channel passivation from ambient species including water molecules. Additionally, the transistor current marginally increased from 1.2 to 1.6  $\mu$ A (Figure S3d in the SI). We speculate that residue of the DMF solvent still remains on the NW shell after DMF treatment of the FET device, and after exposure to air, it still contributes to mild oxidation and to the reduction of hysteresis over a longer period of time. This phenomenon is under further investigation.

An anisole-treated FET device, on the contrary, showed an increase of more than 10 V hysteresis in the initial 24 h period of exposure to air. However, the device current dropped five times during this short exposure, indicating degradation of the FET characteristics (Figure S4 in the SI).

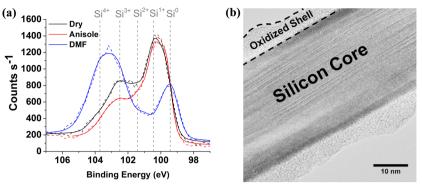

**Figure 3.** (a) High-resolution XPS spectrum of the Si 2p region of SFLS-grown Si NWs dispersed in anisole and DMF. The dashed lines indicate the different oxidation states of Si<sup>0</sup>, Si<sup>+</sup>, Si<sup>2+</sup>, Si<sup>3+</sup>, and Si<sup>4+</sup>. After DMF treatment, the Si<sup>4+</sup> peak increases significantly, while anisole treatment results in a small increase in the silicon peak compared to the dry sample. (b) High-resolution TEM (Hitachi HD-2300A STEM) image of Si NWs dispersed in DMF showing a single-crystal silicon core with 30 nm diameter and a  $\sim$ 5–8-nm-thick amorphous oxidized polyphenylsilane shell.

Overall, the hysteresis behavior in our devices was consistent with previous reports for Si NW FETs, exhibiting an anticlockwise hysteresis when during the forward gate voltage scan the long-lived traps are populated with the majority of the carrier holes, and the FET threshold is then pushed to higher gate voltages, as exhibited by the reverse scan. The traps are considered to be located at the interfacial surface layer of the Si NW channel and the bottom-gated dielectric (SiO<sub>2</sub>). The traps are mainly associated with the defects of the semiconducting nanomaterials, the dielectric surface functionalities, and the adsorbed water and oxygen molecules at/in the interfacial layers.<sup>12</sup> We speculated that DMF treatment is not likely to cause changes in the Si NW core structure, and the observed reduction of hysteresis is associated with the NW polyphenylsilane shell composition.

For investigation of the NW surface passivation, a highresolution XPS technique was used to analyze the surface of the as-synthesized, DMF- and anisole-treated NWs (see the SI for NW characterization). Figure 3a illustrates the peak shapes of the Si 2p spectra of each sample, with the vertical lines showing the five different silicon subpeaks including the spin-splitting peak Si<sup>0</sup> (elemental silicon), the substoichiometric oxides Si<sup>+</sup>  $(Si_2O)$ ,  $Si^{2+}$  (SiO), and  $Si^{3+}$  (Si<sub>2</sub>O<sub>3</sub>), and the silicon dioxide peak Si<sup>4+</sup> (SiO<sub>2</sub>),<sup>24</sup> fitted using the Gaussian/Lorentzian function (Figure S5a-c in the SI), where the peak positions agree with the work of Bashouti et al.<sup>25,26</sup> By overlaying the peak line shapes, we observed a substantial difference in the oxidation states of the DMF-treated Si NW shell compared to the as-synthesized (dry) and anisole-treated Si NWs. Following DMF treatment, the main peak position of the Si 2p highresolution XPS scan shifts from 100.3 (for dry silicon) and 100.1 (for anisole-treated silicon) to 103.2 eV, which corresponds to the formation of  $SiO_2$  (Si<sup>4+</sup>).<sup>24</sup>

In relation to the reference sample (dry NWs), the DMF treatment has the greatest impact on oxidation of the NW shells, showing a 35% increase in the SiO<sub>2</sub> peak (Si<sup>4+</sup>) and further reduction of the other peaks, except the Si<sub>2</sub>O<sub>3</sub> (Si<sup>3+</sup>) peak, which stays relatively constant to the reference (Tables S3 and S4 in the SI). Also, the decrease in the silicon core (Si<sup>0</sup>) peak (-8%) in the DMF-treated NWs suggests that the silica content has also increased compared with the anisole-treated NWs (Si<sup>0</sup> + 6%). Furthermore, the decrease in the Si<sup>+</sup> (-20%) and Si<sup>2+</sup> (-5%) states indicates that the majority of the SiO<sub>2</sub> (Si<sup>4+</sup>) increase comes from the early oxidization stages (Si<sup>+</sup> and Si<sup>2+</sup>; Tables S3 and S4 in the SI).

Anisole-treated NWs, compared to the reference, show a slight decrease in Si<sup>+</sup> and Si<sup>3+</sup>, with a slight increase in the Si<sup>2+</sup> and Si<sup>4+</sup> suboxide peaks (Tables S3 and S4 in the SI, ). This result suggests that the treatment of the NWs using anisole either decreases the Si<sup>+</sup> and Si<sup>3+</sup> oxides or etches the polyphenylsilane shell.

Overall, XPS analysis indicates that DMF treatment decreases the concentration of the Si<sup>+</sup> and Si<sup>2+</sup> species and contributes to the increase of the SiO<sub>2</sub> (Si<sup>4+</sup>) composition in the NW surface layer. Thus, the DMF solution acts as a mild chemical oxidizing agent for the polyphenylsilane shell.<sup>27,28</sup>

According to the C 1s XPS spectra, residues of anisole (Figure S6b in the SI) and DMF (Figure S6c in the SI) can be observed because of increases of the C–C and C=C signatures for anisole due to the presence of the aromatic ring and C=O in DMF.

Following XPS analysis, Si NWs were characterized by highresolution TEM (Hitachi HD-2300A STEM). Figure 3b shows an image of a typical NW, with a 30-nm-diameter single-crystal core. During the NW growth, Si atoms diffuse into gold-seeded nanoparticles and are subsequently extruded, giving rise to a uniform core diameter along the NW, as set by the seed particle size. The light-gray layer around the silicon core indicates the presence of a 5-8-nm-thick oxidized amorphous shell. The increase of the silica amount  $(SiO_2)$  is likely to passivate the silicon core channel area, to provide stability against environmental aging, and to prevent the adsorption of water molecules that are responsible for the hysteretic behavior of the NW FET device. However, it is expected that the nonuniformity of the shell contributes to variations in the low hysteresis behavior of our devices. The shell's nonuniformity (~35% variations in thickness) mainly originates from the local concentration gradients of polyphenylsilane byproducts that are randomly deposited along the NW core, resulting in a thicker shell at high concentrations and a thinner one at low concentrations. As a result, a distribution of the shell thickness both between the NWs and along a single NW is observed. Additionally, the oxide shell can act as a gate dielectric, providing an improvement in the interfacial properties between the Si NW core and the gate dielectric  $(SiO_2)$ . Furthermore, because of the reduction of the trap states after DMF treatment and the corresponding increase of the transistor current (Figure 1b), the FET on/off current ratio between the "on" and "off" states is increased.

# **ACS Applied Materials & Interfaces**

We further investigated whether the passivation mechanism of DMF was applicable to NWs that have already been treated in anisole. Bottom-gated FETs were fabricated with NWs dispersed in anisole and then treated in DMF for a short period of time. The hysteresis reduced from 11 to 6 V when the FET device was dipped into DMF for 10 s, in ambient air (Figure S7a in the SI). An increase of the FET performance was also observed, with the output current  $(I_D)$  increasing from ~0.95 to ~4.3  $\mu$ A (measured in a N<sub>2</sub>-filled glovebox; Figure S7b in the SI) and an increase in the device mobility ( $\mu$ ) from 1 to 8 cm<sup>2</sup>  $V^{-1}$  s<sup>-1</sup>. The reduction of the hysteresis indicates the fast formation of the oxide shell when the NWs are exposed to DMF, providing stability to the FET performance. Then, the device was exposed to ambient conditions for 1000 h, and the hysteresis only marginally increased by 0.6 V with a further increase in the device mobility to 9  $\mbox{cm}^2\ \mbox{V}^{-1}\ \mbox{s}^{-1}$  and in the output current  $(I_D)$  to ~5.8  $\mu$ A (Figure S7c,d in the SI), highlighting the passivation effect of DMF on the polyphenylsilane NW shell. A shift of the threshold voltage to the positive was also observed (Figure S7c in the SI) after the stability test in ambient air, from  $V_{\rm th} = -9$  to -6 V, verifying passivation of the NW interface and reduction/elimination of the number of occupied traps, which cause screening of the gate electric field. On the basis of a statistical analysis of 10 samples, an increase in the device mobility  $(\mu)$  was also observed (Figure S8 in the SI). DMA- and N-methylformamide (NMF)treated Si NWs were also investigated, with DMA demonstrating results similar to those of DMF, but their surface analysis needs further investigation. Also, DMF-treated CVD-grown Si NWs showed results similar to those of DMF-treated SFLSgrown Si NWs, with less than 2 V hysteresis in a N<sub>2</sub> environment and less than 1 V when exposed to ambient conditions, further demonstrating passivation effects of DMF for different types of NWs.

As a final step, we have fabricated bottom-gated Si NW FETs on plastic substrates (Kapton) to investigate the compatibility of DMF passivation for plastic electronic devices. The NW FETs with a parylene N gate insulator and DMF-processed NWs demonstrated hysteresis values ( $\sim 2.5$  V; Figure S9 in the SI) similar to those of the transistors with a SiO<sub>2</sub> dielectric. DMF did not seem to affect the organic gate dielectric or the substrate.

In summary, we have experimentally demonstrated the effect of a DMF solution acting as a mild oxidizing agent and passivation of Si NW shells, resulting in a drastically suppressed NW FET hysteresis. This chemical method can be conducted at room temperature, compatible with the fabrication of NW electronic devices on various substrates including plastics. Bottom-gated FET devices fabricated with Si NWs dispersed in DMF exhibited low hysteresis, on average ~8 times lower as opposed to using anisole as a dispersant. A hysteresis reduction of over 300 times (from 32 to 0.1 V) was demonstrated with near-zero hysteresis devices obtained with DMF-treated SFLS Si NWs.

DMF-treated NWs exhibited a 1-2 order of magnitude trap density decrease compared to anisole-treated NWs and an increase in the device mobility. DMF-treated devices showed environmental stability, with a further decrease of the hysteresis even after 1000 h of exposure as opposed to the anisole-treated devices. However, a sharp increase in hysteresis was observed for anisole-processed NW FETs after exposure to air.

On the basis of the XPS data, a significant 35% increase of the SiO<sub>2</sub> composition of the NW shell around the core is

demonstrated after DMF treatment, passivating the silicon core. The dramatic reduction of hysteresis following the DMF processing indicates that the modified NW shell prevents the adsorption of water molecules on the surface of the silicon core, which is the main source of hysteresis. The shell passivation of Si NWs with DMF considerably improves the fabrication of reliable and reproducible Si NW devices demonstrated with FETs, suitable for printed nanomaterial electronic applications. The NW passivation approach can be extended to other NW applications including supercapacitors, photovoltaics, and photodiodes.

## ASSOCIATED CONTENT

## **S** Supporting Information

The Supporting Information is available free of charge on the ACS Publications website at DOI: 10.1021/acsami.5b07140.

Experimental section for NW FET device fabrication, XPS sample preparation, NW hysteresis measurements and characterization, FET electrical and trap density characterization, XPS spectral analysis, and NW device mobility statistical analysis (PDF)

# AUTHOR INFORMATION

#### Corresponding Author

\*E-mail: m.shkunov@surrey.ac.uk.

#### **Author Contributions**

The manuscript was written through contributions of all authors. All authors have given approval to the final version of the manuscript.

#### Notes

The authors declare no competing financial interest.

## ACKNOWLEDGMENTS

The authors thank Dr. Michael A. Terzidis (ATI, University of Surrey) for the valuable discussion on the NW surface functionalization via DMF. M.S. acknowledges equipment funding from EPSRC UK Grant EP/I017569/1. B.A.K. and T.B. acknowledge funding of this research from the US National Science Foundation (grant no. CHE-1308813) and the Robert A. Welch Foundation (grant no. F-1464).

## REFERENCES

(1) Liu, X.; Long, Y.-Z.; Liao, L.; Duan, X.; Fan, Z. Large-Scale Integration of Semiconductor Nanowires for High-Performance Flexible Electronics. *ACS Nano* **2012**, *6* (3), 1888–1900.

(2) Cui, Y.; Wei, Q.; Park, H.; Lieber, C. M. Nanowire Nanosensors for Highly Sensitive and Selective Detection of Biological and Chemical Species. *Science* **2001**, *293* (5533), 1289–1292.

(3) Gao, A.; Lu, N.; Wang, Y.; Dai, P.; Li, T.; Gao, X.; Wang, Y.; Fan, C. Enhanced Sensing of Nucleic Acids with Silicon Nanowire Field Effect Transistor Biosensors. *Nano Lett.* **2012**, *12* (10), 5262–5268.

(4) Patolsky, F.; Lieber, C. M. Nanowire Nanosensors. *Mater. Today* 2005, 8 (4), 20–28.

(5) Cui, Y.; Zhong, Z.; Wang, D.; Wang, W. U.; Lieber, C. M. High Performance Silicon Nanowire Field Effect Transistors. *Nano Lett.* **2003**, 3 (2), 149–152.

(6) Duan, X.; Niu, C.; Sahi, V.; Chen, J.; Parce, J. W.; Empedocles, S.; Goldman, J. L. High-Performance Thin-Film Transistors Using Semiconductor Nanowires and Nanoribbons. *Nature* **2003**, 425 (6955), 274–278.

(7) Zheng, G.; Lu, W.; Jin, S.; Lieber, C. M. Synthesis and Fabrication of High-Performance N-Type Silicon Nanowire Transistors. *Adv. Mater.* **2004**, *16* (21), 1890–1893.

# **ACS Applied Materials & Interfaces**

(8) Takei, K.; Takahashi, T.; Ho, J. C.; Ko, H.; Gillies, A. G.; Leu, P. W.; Fearing, R. S.; Javey, A. Nanowire Active-Matrix Circuitry for Low-Voltage Macroscale Artificial Skin. *Nat. Mater.* **2010**, *9* (10), 821–826.

(9) McAlpine, M. C.; Ahmad, H.; Wang, D.; Heath, J. R. Highly Ordered Nanowire Arrays on Plastic Substrates for Ultrasensitive Flexible Chemical Sensors. *Nat. Mater.* **2007**, *6* (5), 379–384.

(10) Hanrath, T.; Korgel, B. A. Supercritical Fluid–Liquid–Solid (SFLS) Synthesis of Si and Ge Nanowires Seeded by Colloidal Metal Nanocrystals. *Adv. Mater.* **2003**, *15* (5), 437–440.

(11) Tuan, H.-Y.; Korgel, B. A. Importance of Solvent-Mediated Phenylsilane Decompositon Kinetics for High-Yield Solution-Phase Silicon Nanowire Synthesis. *Chem. Mater.* **2008**, *20* (4), 1239–1241.

(12) Kim, S. H.; Yun, W. M.; Kwon, O.-K.; Hong, K.; Yang, C.; Choi, W.-S.; Park, C. E. Hysteresis Behaviour of Low-Voltage Organic Field-Effect Transistors Employing High Dielectric Constant Polymer Gate Dielectrics. J. Phys. D: Appl. Phys. 2010, 43 (46), 465102.

(13) Todescato, F.; Capelli, R.; Dinelli, F.; Murgia, M.; Camaioni, N.; Yang, M.; Bozio, R.; Muccini, M. Correlation Between Dielectric/ Organic Interface Properties and Key Electrical Parameters in PPV-Based OFETs. J. Phys. Chem. B 2008, 112 (33), 10130–10136.

(14) Kim, W.; Javey, A.; Vermesh, O.; Wang, Q.; Li, Y.; Dai, H. Hysteresis Caused by Water Molecules in Carbon Nanotube Field-Effect Transistors. *Nano Lett.* **2003**, *3* (2), 193–198.

(15) Rosaye, J.-Y.; Kurumado, N.; Sakashita, M.; Ikeda, H.; Sakai, A.; Mialhe, P.; Charles, J.-P.; Zaima, S.; Yasuda, Y.; Watanabe, Y. Characterization of Defect Traps in SiO<sub>2</sub> Thin Films Influence of Temperature on Defects. *Microelectron. J.* **2002**, 33 (5), 429–436.

(16) Wang, Y.; Lew, K.-K.; Mattzela, J.; Redwing, J.; Mayer, T. Top-Gated Field Effect Devices Using Oxidized Silicon Nanowires, *Device Research Conference Digest*, 63rd ed.; IEEE: Piscataway, NJ, 2005; pp 159–160.

(17) Kawashima, T.; Saitoh, T.; Komori, K.; Fujii, M. Synthesis of Si Nanowires with a Thermally Oxidized Shell and Effects of the Shell on Transistor Characteristics. *Thin Solid Films* **2009**, *517* (16), 4520–4526.

(18) Fukata, N.; Kaminaga, J.; Takiguchi, R.; Rurali, R.; Dutta, M.; Murakami, K. Interaction of Boron and Phosphorus Impurities in Silicon Nanowires During Low-Temperature Ozone Oxidation. *J. Phys. Chem. C* **2013**, *117* (39), 20300–20307.

(19) Hughes, M. P. Nanoelectromechanics in Engineering and Biology; CRC Press: Boca Raton, FL, 2002.

(20) Kawaguchi, H.; Taniguchi, M.; Kawai, T. Control of Threshold Voltage and Hysteresis in Organic Field-Effect Transistors. *Appl. Phys. Lett.* **2009**, *94* (9), 093305.

(21) Paska, Y.; Haick, H. Interactive Effect of Hysteresis and Surface Chemistry on Gated Silicon Nanowire Gas Sensors. *ACS Appl. Mater. Interfaces* **2012**, *4* (5), 2604–2617.

(22) Opoku, C.; Hoettges, K. F.; Hughes, M. P.; Stolojan, V.; Silva, S. R. P.; Shkunov, M. Solution Processable Multi-Channel ZnO Nanowire Field-Effect Transistors with Organic Gate Dielectric. *Nanotechnology* **2013**, *24* (40), 405203.

(23) Dattoli, E. N.; Wan, Q.; Guo, W.; Chen, Y.; Pan, X.; Lu, W. Fully Transparent Tthin-Film Transistor Devices Based on SnO<sub>2</sub> Nanowires. *Nano Lett.* **2007**, *7* (8), 2463–2469.

(24) Watts, J. F.; Wolstenholme, J. An Introduction to Surface Analysis by XPS and AES; Wiley-VCH: New York, 2003; p 224, ISBN 0-470-84713-1.

(25) Bashouti, M. Y.; Sardashti, K.; Ristein, J.; Christiansen, S. Kinetic Study of H-Terminated Silicon Nanowires Oxidation in Very First Stages. *Nanoscale Res. Lett.* **2013**, *8* (1), 41.

(26) Bashouti, M. Y.; Sardashti, K.; Ristein, J.; Christiansen, S. H. Early Stages of Oxide Growth in H-Terminated Silicon Nanowires: Determination of Kinetic Behavior and Activation Energy. *Phys. Chem. Chem. Phys.* **2012**, *14* (34), 11877–11881.

(27) Song, J. H.; Sailor, M. J. Dimethyl Sulfoxide as a Mild Oxidizing Agent for Porous Silicon and its Effect on Photoluminescence. *Inorg. Chem.* **1998**, 37 (13), 3355–3360.

(28) Urata, T.; Fukami, K.; Sakka, T.; Ogata, Y. H. Pore Formation in P-Type Silicon in Solutions Containing Different Types of Alcohol. *Nanoscale Res. Lett.* **2012**, *7* (1), 329.